Prozessorgeflüster

Von Makro-, Mega- und Mikroprozessoren

AMDs Serverprozessor Naples wirft seine Schatten voraus, die Chinesen basteln an allem und die Briten sind immer für eine Überraschung gut.

Einen Stand hatte AMD diesmal auf der ISC2016 (siehe S. 16) nicht, aber immerhin gab es für geladene Gäste eine spannende Präsentation hinter den Kulissen. Presse war da selbstredend unerwünscht, aber auf der ISC spricht sich bekanntlich dennoch alles herum. Tatsächlich konnte AMD nämlich schon einige A0-Prototypen des Server-Chips mit Zen-Architektur namens Naples (Neapel) vorzeigen und die geladenen Wissenschaftler damit auch durchaus beeindrucken. Alles, was CERN-Ingenieur Liviu Vâlsan und Fuad Abazovic auf Fudzilla.com bereits vorab ausgeplaudert hatten, scheint nach dem, was man auf der ISC vernahm, den Tatsachen zu entsprechen.

Vier Versionen soll es von Naples geben, darunter insbesondere auch den großen „Naples for Enterprise Servers“ mit 32 Kernen, 64 Threads und 64 MByte L3-Cache. Der könnte dem ebenfalls für 2017 vorgesehenen Skylake EP/EX mit seinen maximal 28 Kernen dann recht gut Paroli bieten, auch wenn ihm das i-Tüpfelchen, AVX512 (jedenfalls in Hardware), fehlt.

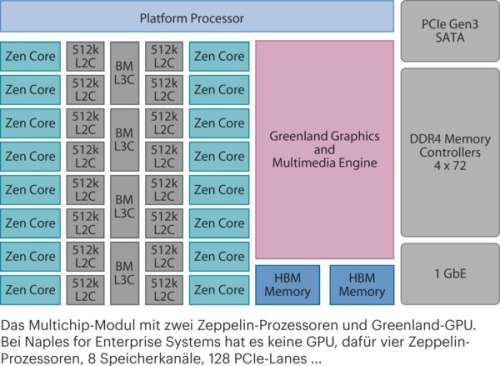

Wie der Enterprise-Naples intern organisiert ist, ist noch unklar. In ihm stecken offenbar vier Prozessoren namens Zeppelin (Family 17, Model 0), ein jeder mit acht Zen-Kernen. Vier Kerne teilen sich dabei einen L3-Cache von 8 GByte. Vermutlich zwei solcher Zeppeline packt AMD auf einen Chip und für den Enterprise Server kommen dann zwei solcher Chips auf ein Multichip-Modul. Es könnten aber auch vier einzelne Dice sein.

Ein jeder Zeppelin-Prozessor besitzt zwei DDR4 Speicherkanäle, 32 PCIe-Lines, acht SATA/NVME-Anschlüsse und vier 10GbE-Anschlüsse. Damit lassen sich an dem Enterprise-Modul insgesamt acht Speicherkanäle und mit 128 PCIe-Lanes bis zu acht GPUs ohne lästige PCIe-Switches anschließen.

Mit solchen Daten, insbesondere mit der hohen Speicherbandbreite, sieht es also so schlecht nicht aus für den Server-Chip, wenn er denn im Verlauf von 2017 auch wirklich herauskommt.

Die kleinere Naples-Version mit insgesamt 16 Kernen besteht aus zwei Zeppelin-Prozessoren auf einem Chip. Mit ihr ist dann auch ein MCM mit einer schnellen Vega-GPU (Greenland) mit 4 TFlops geplant – ebenfalls sehr interessant für HPC.

Und schließlich gibt es noch kleinere Ausführungen mit nur zwei, vier oder acht Kernen. Hergestellt wird Naples so wie Polaris und demnächst Vega in dem von Samsung lizenzierten 14-nm-FinFet-Prozess bei Globalfoundries in New York.

Findige Leute haben übrigens auf den Importlisten von Taiwan nach Bangalore/Indien am 8. und 20. Juni schon diverse Test-Boards mit Naple-Prozessoren mit 2,4 GHz Takt entdeckt – wenn auch nur mit USB 2.0.

Und SPARC?

Nach dem auf der ISC bekanntgegebenen Wechsel bei Fujitsu von SPARC64 zu ARMv8 sieht es um die Zukunft von SPARC eher trübe aus. Oracle hält aber weiter daran fest, die aktuelle Roadmap geht bis 2019, mit neuen Kernen für die T-, M- und S-Linien. Der im vorigen Jahr auf der Hot Chips vorgestellte „Advanced Low-Cost Processor“ Sonoma (SPARC S7) mit insgesamt acht Kernen, vier DDR4-Speicherkanälen, zweimal InfiniBand-FDR und 16 PCIe-Lanes (Gen 3) kommt jetzt in neuen S7-Systemen auf den Markt. Am High-End konnte sich der im Herbst letzten Jahres herausgekommene 32-Kerner M7 ganz gut einbringen, eroberte mit seiner Kernmacht und mit dem hohem Takt von 4,1 GHz die Spitze bei vielen Industrie-Benchmarks, so auch bei SPECfp in Single-Socket-Systemen – wo ihn Intels neuer Xeon Phi KNL kürzlich entthronte (SPECint hält er noch).

Und dann gibt es ja noch die Chinesen, die inzwischen den schnellsten Rechner der Welt mit dem ShenWei-26010-Prozessor aus heimischer Produktion betreiben. Dem ShenWei sagt man eine Nähe zum Alpha-Prozessor nach, wiewohl das die Betreiber vehement bestreiten. Daneben erproben die Chinesen aber auch andere Architekturen, mit FeiTeng eben auch eine mit SPARCv9. 2048 FeiTeng-1000-Prozessoren (8 Kerne, 1 GHz, 65 nm) laufen bereits seit Jahren im Tianhe-1A-Supercomputer nebenbei mit, nur kurzzeitig unterbrochen von einer großen Explosion in Tianjin im vorigen Jahr. Im Tianhe-2-Komplex sollen 4096 schnellere FeiTeng-1500-Prozessoren (16 Kerne, 1,8 GHz, 65 W TDP, 40 nm) ackern. Aber auch beim FeiTeng scheint das Ende der SPARC-Fahnenstange erreicht und die Architektur muss hinfort ARMv8 weichen. Der FeiTeng-1500A jedenfalls soll bereits mit 16 ARMv8-Kernen (Mars) von Phytium bestückt sein.

Immer mal wieder werfen auch die MIPS-kompatiblen Loongson-Prozessoren (früher Godson genannt) Schlaglichter, vor allem in den Vorträgen von Professor Weiwu Hu. Den Vierkerner Loongson 3B hatte er für 2011 angekündigt, im August 2015 kamen dann der 3A2000 (für Desktop-PCs) und der 3B2000 (für Server) mit 1,5 GHz Takt tatsächlich heraus, wurden aber außerhalb Chinas bislang kaum gesichtet. In diesem Jahr sollen die Loongson-3B3000-Versionen mit höherem Takt folgen. Die sogenannten GS464/E-Kerne arbeiteten mit MIPS64 beziehungsweise LoongISA v1. Sie können auch ARM- und x86- Code durch hardwareunterstützte Binary Translation ausführen. Chefarchitekt Hu kümmerte sich aber derweil mehr um Fernseh-Chips für Hisense – ein großer chinesischer Elektrokonzern, der hierzulande durch sein Sponsorship für Schalke 04 und vor allem für die aktuelle EM16 aufgefallen sein dürfte. (as@ct.de)